Visible to Intel only — GUID: llx1507945752507

Ixiasoft

1. Design Example Quick Start Guide for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

2. Design Example Description for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

3. Document Revision History for External Memory Interfaces Intel® Cyclone® 10 GX FPGA IP Design Example User Guide

1.1. Creating an EMIF Project

1.2. Generating and Configuring the EMIF IP

1.3. Generating the Synthesizable EMIF Design Example

1.4. Generating the EMIF Design Example for Simulation

1.5. Simulation Versus Hardware Implementation

1.6. Simulating External Memory Interface IP With ModelSim

1.7. Pin Placement for Intel® Cyclone® 10 GX EMIF IP

1.8. Compiling and Programming the Intel® Cyclone® 10 GX EMIF Design Example

1.9. Debugging the Intel® Cyclone® 10 GX EMIF Design Example

Visible to Intel only — GUID: llx1507945752507

Ixiasoft

1.3. Generating the Synthesizable EMIF Design Example

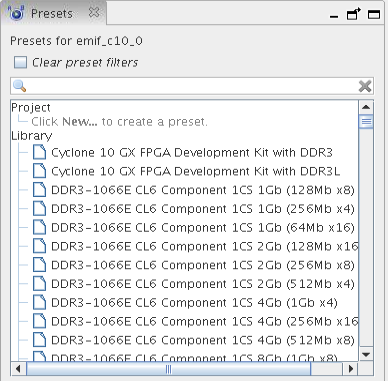

For the Intel® Cyclone® 10 GX development kits, there are presets that automatically parameterize the EMIF IP and generate pinouts for the specific board.

- Verify that the Presets window is visible. If the Presets window is not visible, display it by selecting View > Presets.

- In the Presets window, select the appropriate development kit preset and click Apply.

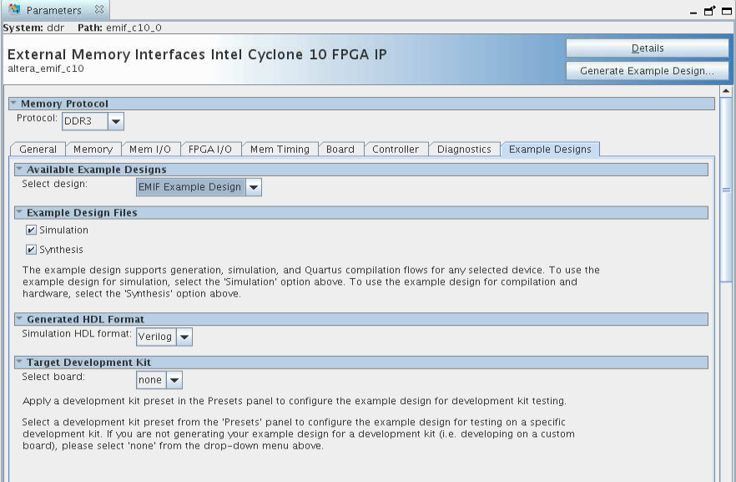

- Configure the EMIF IP and click Generate Example Design in the upper-right corner of the window.

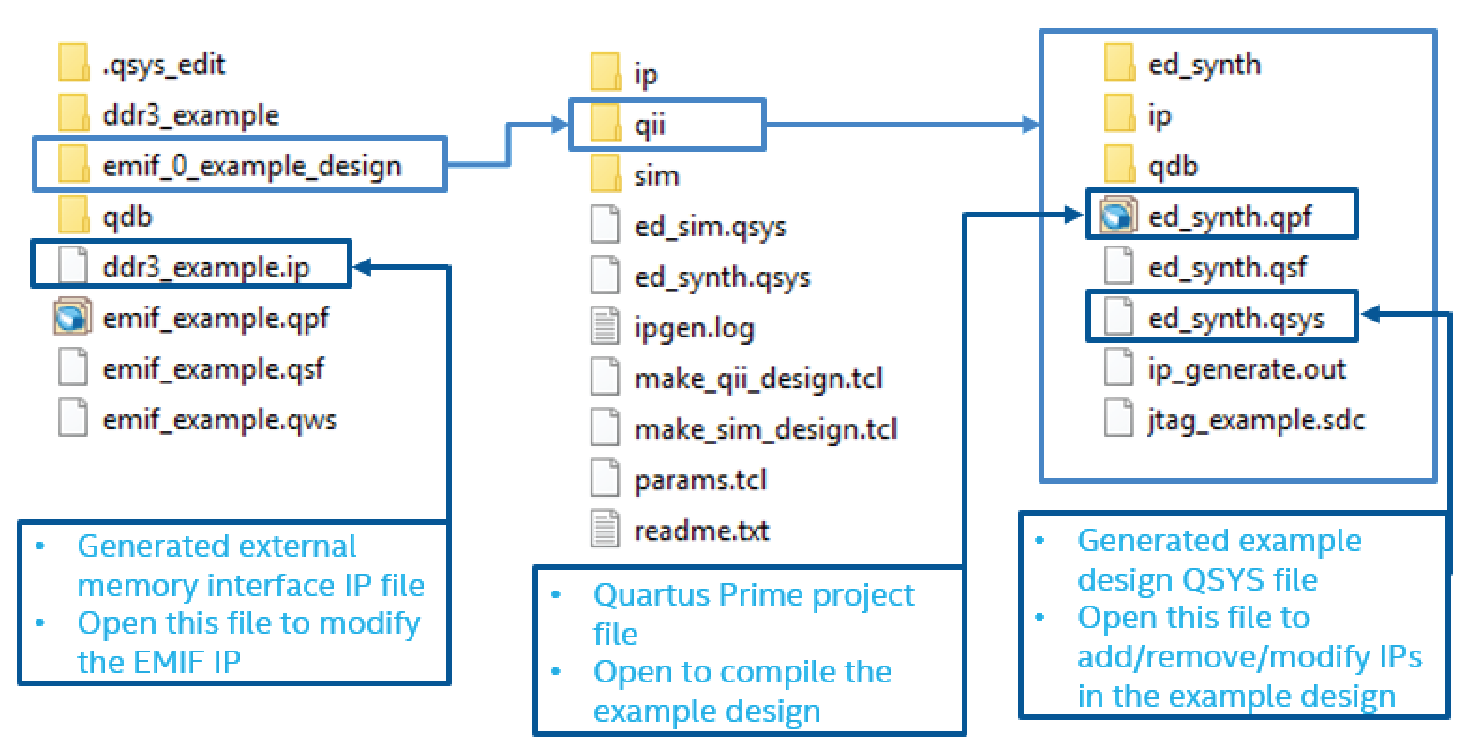

- Specify a directory for the EMIF design example and click OK. Successful generation of the EMIF design example creates the following fileset under a qii directory.

Figure 3. Generated Synthesizable Design Example File Structure

Note:

If you don't select the Simulation or Synthesis checkbox, the destination directory will contain Platform Designer design files, which are not compilable by the Intel® Quartus® Prime software directly, but can be viewed or edited under the Platform Designer. In this situation you can run the following commands to generate synthesis and simulation file sets.

- To create a compilable project, you must run the quartus_sh -t make_qii_design.tcl script in the destination directory.

- To create a simulation project, you must run the quartus_sh -t make_sim_design.tcl script in the destination directory.