Visible to Intel only — GUID: vrg1511996057567

Ixiasoft

Visible to Intel only — GUID: vrg1511996057567

Ixiasoft

4.1.5. Avalon® Streaming Interfaces

Avalon® Streaming ( Avalon® ST) interfaces support a unidirectional flow of data, and are typically used for components that drive high-bandwidth and low-latency data.

struct int_v8 {

int data[8];

};

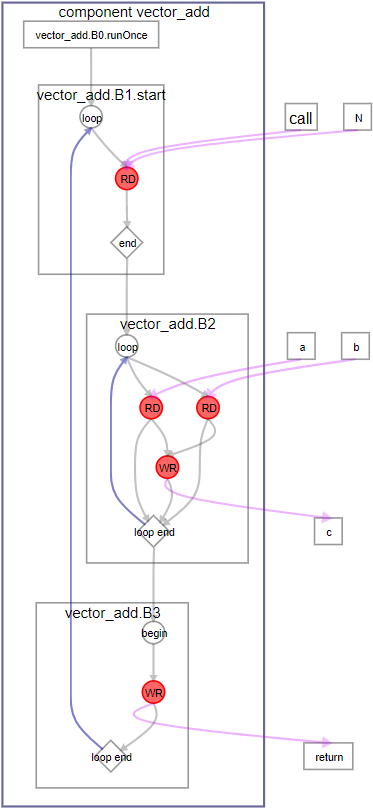

component void vector_add(

ihc::stream_in<int_v8>& a,

ihc::stream_in<int_v8>& b,

ihc::stream_out<int_v8>& c,

int N) {

for (int j = 0; j < (N/8); ++j) {

int_v8 av = a.read();

int_v8 bv = b.read();

int_v8 cv;

#pragma unroll 8

for (int i = 0; i < 8; ++i) {

cv.data[i] = av.data[i] + bv.data[i];

}

c.write(cv);

}

}

An Avalon® ST interface has a data bus, and ready and busy signals for handshaking. The struct is created to pack eight integers so that eight operations at a time can occur in parallel to provide a comparison with the examples for other interfaces. Similarly, the loop count is divided by eight.

The streaming interfaces are stallable from the upstream sources and the downstream output. Because the interfaces are stallable, the loop initiation interval (II) is approximately 1 (instead of exactly 1). If the component does not receive any bubbles (gaps in data flow) from upstream or stall signals from downstream, then the component achieves the desired II of 1.

If you know that the stream interfaces will never stall, you can further optimize this component by taking advantage of the usesReady and usesValid stream parameters.

| QoR Metric | Pointer | Avalon® MM Host | Avalon® MM Agent | Avalon® ST |

|---|---|---|---|---|

| ALMs | 15593.5 | 643 | 490.5 | 314.5 |

| DSPs | 0 | 0 | 0 | 0 |

| RAMs | 30 | 0 | 48 | 0 |

| fMAX (MHz)2 | 298.6 | 472.37 | 498.26 | 389.71 |

| Latency (cycles) | 24071 | 142 | 139 | 134 |

| Initiation Interval (II) (cycles) | ~508 | 1 | 1 | 1 |

| 1The compilation flow used to calculate the QoR metrics used Quartus® Prime Pro Edition Version 17.1. |

| 2The fMAX measurement was calculated from a single seed. |