Power Rails

You should extract the power rails that your design requires. Your power tree only needs to supply power to the used power rails. It is unlikely that all of your FPGA resource blocks are in use, even in a heavily-loaded design.

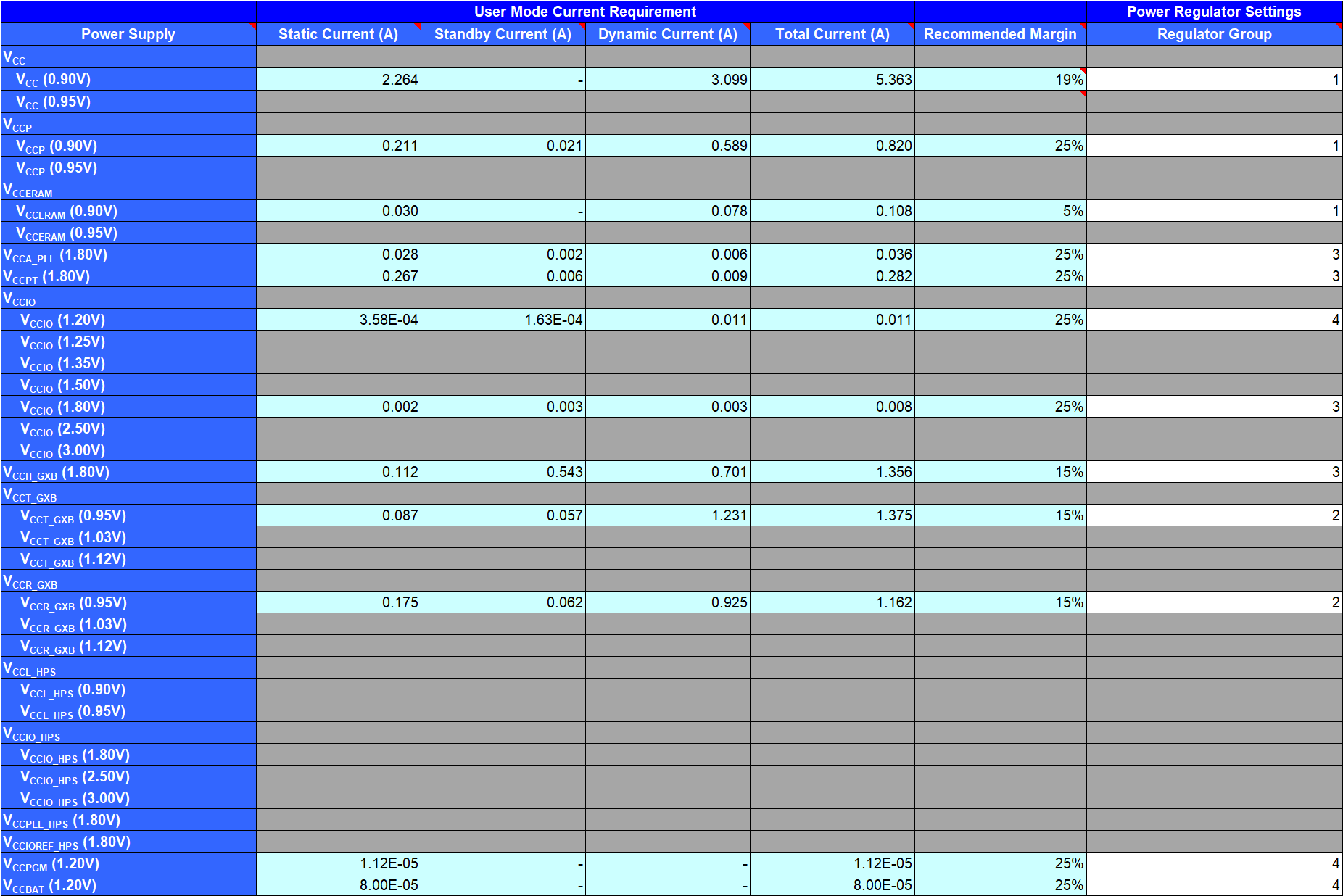

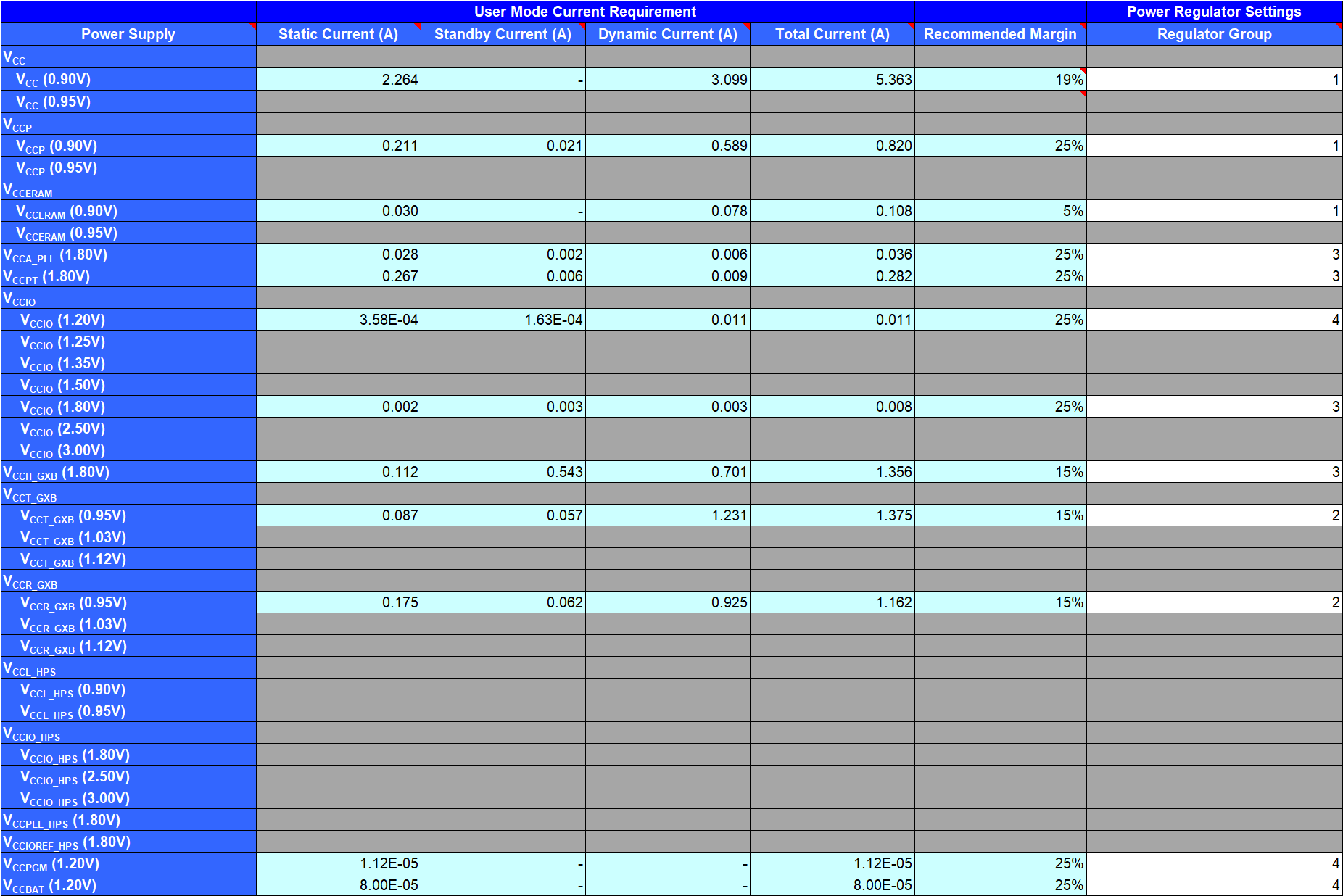

The Report tab in the Early Power Estimator (EPE) spreadsheet describes the expected voltage and current requirements for each FPGA power rail based on your design. The EPE spreadsheet indicates which FPGA power rails require a power supply in two ways:

- The FPGA input line has a non-zero value in the Total Current (A) column.

- For EPE spreadsheet versions 18.0 and later, the FPGA input line has an assigned (not gray) entry in the Power Regulator Settings Regulator Group column next to the Total Current (A) column.

Figure 2. ICCIO Section Call Out from the EPE Spreadsheet Report TabThis figure shows the Report tab of the EPE spreadsheet highlighting utilized inputs. Some inputs, such as FPGA I/O (ICCIO), are generic inputs that may have a total current value that is the sum of the currents required for various I/O inputs at different voltage levels. In this case, while the individual ICCxx rows indicate the various I/O input currents at each voltage level. In this example, you must use different power rail groupings for the ICCIO (1.2 V) and ICCIO (1.8 V) power rails.

You must identify the power rails requiring power in your design before creating a group of the power rails.