Visible to Intel only — GUID: lbl1415395901403

Ixiasoft

Visible to Intel only — GUID: lbl1415395901403

Ixiasoft

1.5. Avalon-ST Example Designs

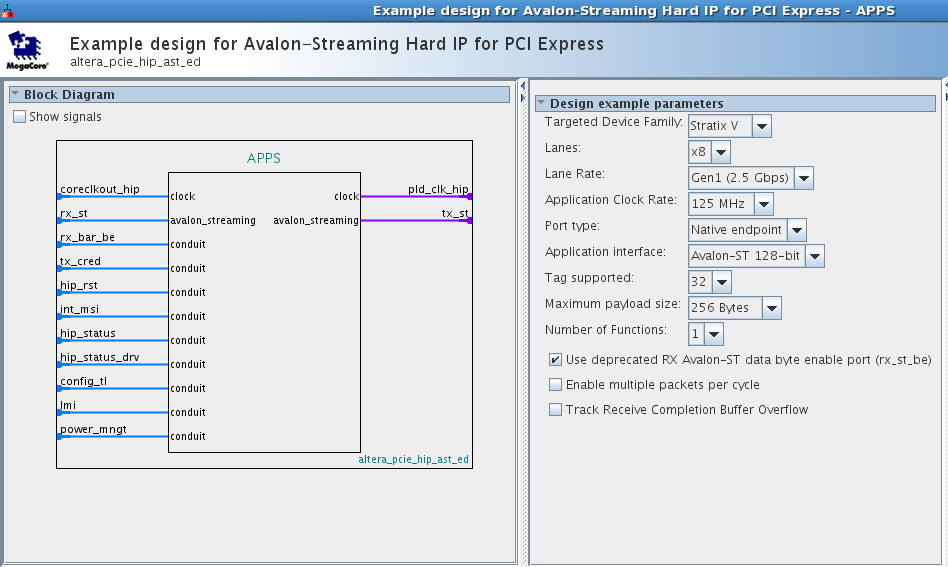

Altera provides example designs to familiarize you with the available functionality. Each design connects the device under test (DUT) to an application programming platform (APP), labeled APPs in the figure below. Certain critical parameters of the APPs component are set to match the values of the DUT. If you change these parameters, you must change the APPs component to match. You can change the values for all other parameters of the DUT without editing the APPs component.

In this example design, the following parameters must be set to match the values set in the DUT:

- Targeted Device Family

- Lanes

- Lane Rate

- Application Clock Rate

- Port type

- Application Interface

- Tags supported

- Maximum payload size

The following Qsys example designs are available for the Stratix V Hard IP for PCI Express. You can download them from the <install_dir>/ ip/altera/altera_pcie/altera_pcie_hip_ast_ed/example_design/<dev> directory:

- pcie_de_gen1_x4_ast64.qsys

- pcie_de_gen1_x8_ast128.qsys

- pcie_de_gen2_x8_ast256.qsys

- pcie_de_gen3_x1_ast64.qsys

- pcie_de_gen3_x4_ast128.qsys

- pcie_de_gen3_x8_ast256.qsys

- pcie_de_rp_gen1_x4_ast64.qsys

- pcie_de_rp_gen1_x8_ast128.qsys