Visible to Intel only — GUID: joc1463362604091

Ixiasoft

Visible to Intel only — GUID: joc1463362604091

Ixiasoft

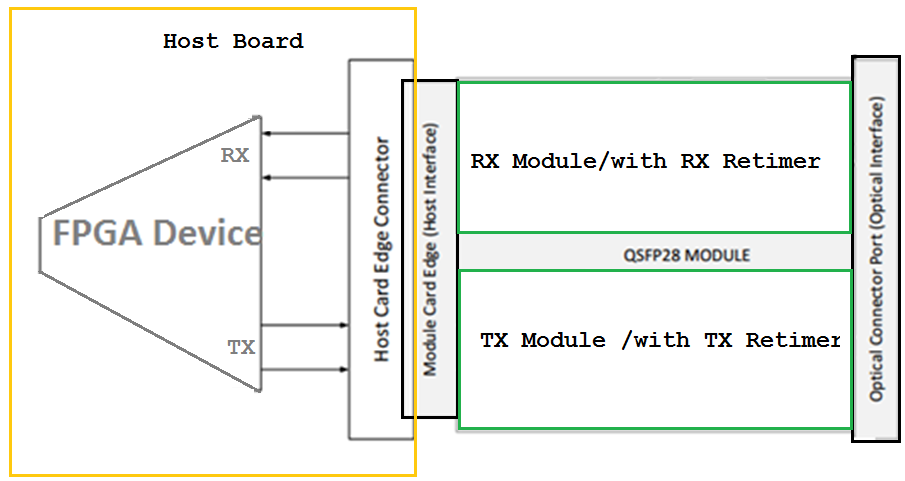

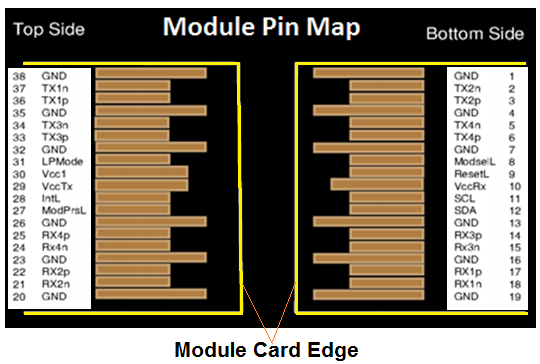

QSFP+ Module Assembly and Pinout

The Quad Small Form-factor Pluggable (QSFP) specification is based on the SFF-8665, SFF-8679 and OIF CEI v3.1 standards.

The roadmap for QSFP+ standards operating up to 28 Gbps includes:

- 10 Gbps QSFP10 SFF-8635

- 14 Gbps QSFP14 SFF-8685

- 28 Gbps QSFP28 SFF-8665

The RX(n)(p/n) and TX(n)(p/n) are module receiver data outputs and transmitter data inputs. They are all AC-coupled 100 Ω differential lines that should be terminated with 100 Ω differentially at the Host ASIC (SerDes). The AC coupling is inside the module and not required on the host board. For operation at 28 Gbps the relevant standards (OIF-CEI-03.1 standard document) define the signal requirements on the high-speed differential lines. For operation at lower rates, refer to the appropriate standards.