Visible to Intel only — GUID: vgo1449736080450

Ixiasoft

Visible to Intel only — GUID: vgo1449736080450

Ixiasoft

1.5.2. Design Verification

- Arria® 10 FPGA development kit

- Loopback FPGA Mezzanine Card (FMC) attached to the FMC port B (FMCB)

- Intel® FPGA Download Cable II

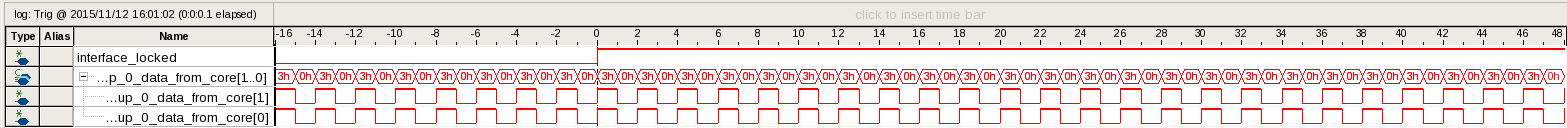

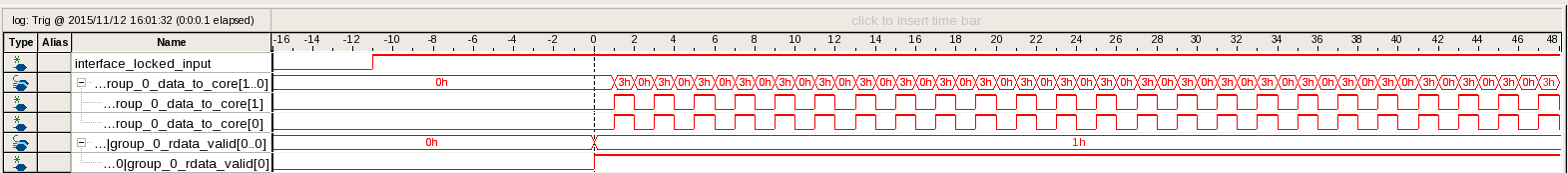

The design example demonstrates a simple loopback that loops back the fixed serial 1100 pattern transmitted from the Altera PHYLite output (ddr_out) to the Altera PHYLite input (ddr_in) through the Loopback FMC daughter card.

The Altera PHYLite output signals from the dataout and clkout pins connect directly to the data_in and strobe_in pins that feed the Altera PHYLite input.

The data received from the Altera PHYLite input after you program the SOF in the Signal Tap Logic Analyzer should be the same as the data transmitted from the IP core through the Altera PHYLite output.