Visible to Intel only — GUID: mta1444889026739

Ixiasoft

Visible to Intel only — GUID: mta1444889026739

Ixiasoft

4.3.2. Model 2: Acknowledgment Model

The acknowledgment model uses an event-driven mechanism. It is used for applications with strict timing requirements. Instead of waiting for a minimum assertion time of 70 μs for tx_analogreset and rx_analogreset, you must wait to receive the acknowledgment from the Transceiver Native PHY IP core to ensure successful assertion and deassertion of the analog resets.

To enable the acknowledgment model, enable the following ports in the Transceiver Native PHY IP core:

- Enable the tx_analog_reset_ack port in the TX PMA

Figure 210. Enabling the tx_analog_reset_ack Port

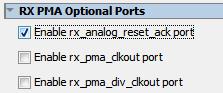

- Enable the rx_analog_reset_ack port in the RX PMA

Figure 211. Enabling the rx_analog_reset_ack Port

tx_analog_reset_ack and rx_analog_reset_ack must be treated as asynchronous signals. You must pass them through a synchronizer before sending them to control logic.