Visible to Intel only — GUID: qnx1522430362650

Ixiasoft

1. E-Tile Transceiver PHY Overview

2. Implementing the Transceiver PHY Layer

3. E-Tile Transceiver PHY Architecture

4. Clock Network

5. PMA Calibration

6. Resetting Transceiver Channels

7. Dynamic Reconfiguration

8. Dynamic Reconfiguration Examples

9. Register Map

10. Debugging E-Tile Transceiver Links

A. E-Tile Channel Placement Tool

B. PMA Direct PAM4 30 Gbps to 57.8 Gbps Implementation

C. Signal Detect Algorithm

D. Detailed Steps for Reconfiguring from Mission Mode to Channel Protection Mode

E. Detailed Steps for Reconfiguring from Channel Protection Mode to Mission Mode

F. Hold Timing Violation

2.2.1. General and Datapath Parameters

2.2.2. PMA Parameters

2.2.3. Core Interface Options

2.2.4. PMA Interface

2.2.5. PMA Adaptation Parameters

2.2.6. Reed Solomon Forward Error Correction (RS-FEC) Parameters

2.2.7. Reset Parameters

2.2.8. Dynamic Reconfiguration Parameters

2.2.9. Deskew Logic

2.2.10. Port Information

2.2.11. PLL Mode

2.2.12. Simplex Support

3.1.1. Transmitter PMA

3.1.2. Receiver PMA

3.1.3. PMA Tuning

3.1.4. Duplex Adaptation Flow

3.1.5. RX Simplex Adaptation Flow

3.1.6. Dynamic Reconfiguration Adaptation Flow

3.1.7. Loopback modes

3.1.8. PMA Interface

3.1.9. TX PMA Bonding

3.1.10. Unused Transceiver Channels

3.1.11. Low Power Mode (LPM)

3.1.10.1. Unused Transceiver Channels in a Used Tile

3.1.10.2. Unused Transceiver Channels in Completely Unused Tiles

3.1.10.3. Unused Transceiver Channels in High-Speed PAM4 Mode

3.1.10.4. Reconfiguring from Mission Mode to Channel Protection Mode

3.1.10.5. Reconfiguring from Channel Protection Mode to Mission Mode

4.2.1. Single 25 Gbps PMA Direct Channel (with FEC) Within a Single FEC Block

4.2.2. Single 10 Gbps PMA Direct Channel (without FEC)

4.2.3. Four 25 Gbps PMA Direct Channel (with FEC) within a Single FEC Block

4.2.4. PMA Direct 25 Gbps x 4 (FEC Off)

4.2.5. PMA Direct 10.3125 Gbps x 4

4.2.6. PMA Direct 100GE Gbps (25 Gbps x 4) (FEC On)

4.2.7. PMA Direct 100GE PAM4 (50 Gbps x 2) (Aggregate FEC On)

4.2.8. PMA Direct High Data Rate (FEC Off)

6.1. When Is Reset Required?

6.2. How Do I Reset?

6.3. Reset Block Architecture

6.4. PMA Analog Reset

6.5. High Level Specification

6.6. Master-Slave Clocking Option 2 Reset Details

6.7. Quartus® Prime Instantiated Transceiver Reset Sequencer

6.8. Block Diagrams

6.9. Interfaces

6.10. Resetting Transceiver Channels Revision History

7.1. Dynamically Reconfiguring Channel Blocks

7.2. Dynamic Reconfiguration Maximum Data Rate Switch

7.3. Interacting with the Dynamic Reconfiguration Interface

7.4. Unsupported Features

7.5. Reading from the Dynamic Reconfiguration Interface

7.6. Writing to the Dynamic Reconfiguration Interface

7.7. Multiple Reconfiguration Profiles

7.8. Arbitration

7.9. Recommendations for PMA Dynamic Reconfiguration

7.10. Steps to Perform Dynamic Reconfiguration

7.11. PMA Attribute Details

7.12. Dynamic Reconfiguration Flow for Special Cases

7.13. Ports and Parameters

7.14. Embedded Debug Features

7.15. Timing Closure Recommendations

7.16. Transceiver Register Map

7.17. Loading IP Configuration Settings

7.18. Dynamic Reconfiguration Revision History

8.1. Reconfiguring the Duplex PMA Using the Reset Controller in Automatic Mode

8.2. PRBS Usage Model

8.3. PMA Error Injection

8.4. PMA Receiver Equalization Adaptation Usage Model

8.5. User-Defined Pattern Example

8.6. Configuring the Attenuation Value (VOD)

8.7. Configuring the Post Emphasis Value

8.8. Configuring pretap1 Values

8.9. Inverting TX Polarity for the PMA Driver

8.10. Inverting RX Polarity for the PMA Driver

8.11. Configuring a PMA Parameter Tunable by the Adaptive Engine

8.12. Configuring a PMA Parameter Using Native PHY IP

8.13. Enabling Low Power Mode for Multiple Channels

8.14. Initializing an RX

8.15. Resetting the RX Equalization

8.16. Dynamic Reconfiguration Examples Revision History

9.2.1. 0x0001: PMA Enable/Disable

9.2.2. 0x0002: PMA PRBS Settings

9.2.3. 0x0003: Data Comparison Set Up and Start/Stop

9.2.4. 0x0005: TX Channel Divide By Ratio

9.2.5. 0x0006: RX Channel Divide By Ratio

9.2.6. 0x0008: Internal Serial Loopback and Reverse Parallel Loopback Control

9.2.7. 0x000A: Receiver Tuning Controls

9.2.8. 0x000E: RX Phase Slip

9.2.9. 0x0011: PMA TX/RX Calibration

9.2.10. 0x0013: TX/RX Polarity and Gray Code Encoding

9.2.11. 0x0014: TX/RX Width Mode

9.2.12. 0x0015: TX Equalization

9.2.13. 0x0017: Error Counter Reset

9.2.14. 0x0018: Status/Debug Register

9.2.15. 0x0019: Status/Debug Register Next Write Field

9.2.16. 0x001A: Status/Debug Register Next Read Field

9.2.17. 0x001B: TX Error Injection Signal

9.2.18. 0x001C: Incoming RX Data Capture

9.2.19. 0x001E: Error Count Status

9.2.20. 0x0020: Electrical Idle Detector

9.2.21. 0x002B: RX Termination and TX Driver Tri-state Behavior

9.2.22. 0x0030: PMA Mux Clock Swap

9.2.23. 0x0126: Read Receiver Tuning Parameters

9.2.24. Reading and Writing PMA Analog Parameters Using Attributes

9.2.24.1. Reading PMA Analog Parameters

9.2.24.2. Updating PMA Analog Parameters

9.2.24.3. Loading Parameters into the Receiver

9.2.24.4. Fixing Parameter Values

9.2.24.5. Reading NRZ/PAM4 Eye Height

9.2.24.6. Enabling and Disabling Electrical Idle Detector Filtering and Reading Electrical Idle Detector Status

9.2.24.7. Initial Adaptation Effort Levels

9.5.1. rsfec_top_clk_cfg

9.5.2. rsfec_top_tx_cfg

9.5.3. rsfec_top_rx_cfg

9.5.4. tx_aib_dsk_conf

9.5.5. rsfec_core_cfg

9.5.6. rsfec_lane_cfg

9.5.7. tx_aib_dsk_status

9.5.8. rsfec_debug_cfg

9.5.9. rsfec_lane_tx_stat

9.5.10. rsfec_lane_tx_hold

9.5.11. rsfec_lane_tx_inten

9.5.12. rsfec_lane_rx_stat

9.5.13. rsfec_lane_rx_hold

9.5.14. rsfec_lane_rx_inten

9.5.15. rsfec_lanes_rx_stat

9.5.16. rsfec_lanes_rx_hold

9.5.17. rsfec_lanes_rx_inten

9.5.18. rsfec_ln_mapping_rx

9.5.19. rsfec_ln_skew_rx

9.5.20. rsfec_cw_pos_rx

9.5.21. rsfec_core_ecc_hold

9.5.22. rsfec_err_inj_tx

9.5.23. rsfec_err_val_tx

9.5.24. rsfec_corr_cw_cnt (Low)

9.5.25. rsfec_corr_cw_cnt (High)

9.5.26. rsfec_uncorr_cw_cnt (Low)

9.5.27. rsfec_uncorr_cw_cnt (High)

9.5.28. rsfec_corr_syms_cnt (Low)

9.5.29. rsfec_corr_syms_cnt (High)

9.5.30. rsfec_corr_0s_cnt (Low)

9.5.31. rsfec_corr_0s_cnt (High)

9.5.32. rsfec_corr_1s_cnt (Low)

9.5.33. rsfec_corr_1s_cnt (High)

10.1. E-Tile Transceiver Toolkit Overview

10.2. E-Tile Transceiver Debugging Flow Walkthrough

10.3. Modifying the Design to Enable E-Tile Transceiver Debug

10.4. Programming the Design into an Intel FPGA

10.5. Loading the Design in the E-Tile Transceiver Toolkit

10.6. Verifying E-Tile Hardware Connections

10.7. Running Transceiver Tests

10.8. Controlling PMA Analog Settings

10.9. Debugging E-Tile Transceiver Links Revision History

B.1. Building Blocks and Considerations

B.2. Starting a New Quartus® Prime Pro Edition Design

B.3. Selecting the Configuration Clock Source

B.4. Instantiating the Transceiver Native PHY IP

B.5. Instantiating the In-system Sources and Probes Intel® FPGA IP

B.6. Making the Top Level Connection

B.7. Assigning Pins

B.8. Bringing up the Board

B.9. Debug Tools

B.10. PMA Direct PAM4 30 Gbps to 57.8 Gbps Implementation Revision History

Visible to Intel only — GUID: qnx1522430362650

Ixiasoft

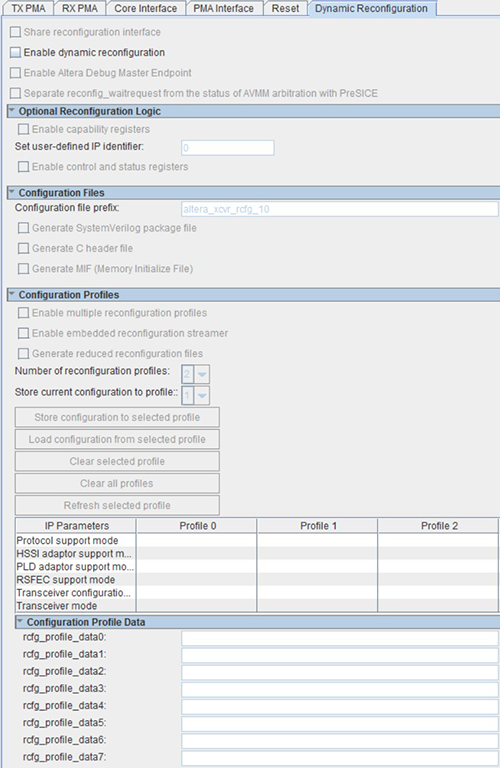

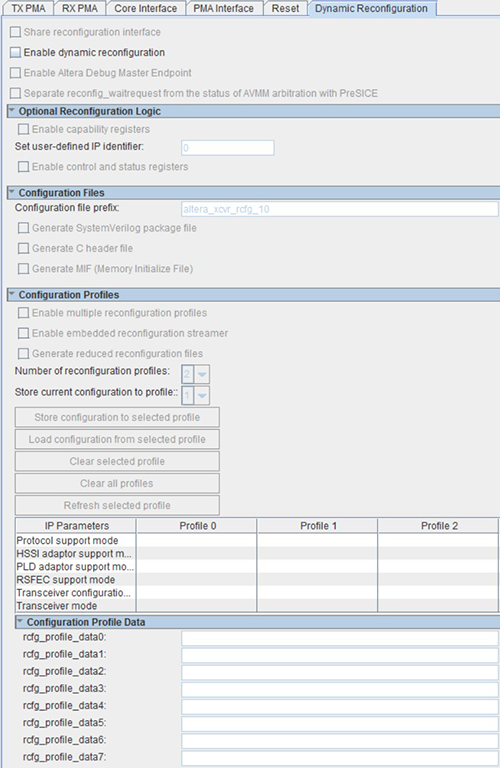

2.2.8. Dynamic Reconfiguration Parameters

Dynamic reconfiguration is the process of modifying transceiver channels to meet changing requirements during device operation.

You can customize channels by triggering reconfiguration during device operation or after device configuration.

Figure 35. Dynamic Reconfiguration Options

| Parameter | Value | Description |

|---|---|---|

| Enable dynamic reconfiguration | On/Off | Enables the dynamic reconfiguration interface. |

| Share reconfiguration interface | On/Off | When enabled, the Native PHY presents a single Avalon® memory-mapped interface slave for dynamic reconfiguration of all channels. In this configuration, the upper [n-1:19] address bits of the reconfiguration address bus specify the selected channel, where 'n' is the log base 2 of the number of channels. Address bits [18:0] provide the register offset address within the reconfiguration space of the selected channel. |

| Enable Native PHY Debug Master Endpoint | On/Off | When enabled, the Native PHY includes an embedded Native PHY Debug Master Endpoint (NPDME) that connects internally to the Avalon® memory-mapped interface slave. The NPDME accesses the reconfiguration space of the transceiver and performs certain test and debug functions via JTAG using the System Console. This option requires you to enable the Share reconfiguration interface option for configurations using more than one channel and may also require that you include a jtag_debug link in the system. |

| Separate reconfig_waitrequest from the status of Avalon® memory-mapped interface arbitration | On/Off | When enabled, the reconfig_waitrequest does not indicate the status of Avalon® memory-mapped interface arbitration. The Avalon® memory-mapped interface arbitration status is reflected in a soft status register bit. This feature requires that you enable the Enable control and status registers feature under Optional Reconfiguration Logic. The default setting is Off. |

| Enable capability registers | On/Off | Enables capability registers, which provide high level information about the transceiver configuration. Refer to the PMA Capability Registers section. |

| Set user-defined IP identifier | 0 | Sets a user-defined numeric identifier that can be read from the user_identifer offset when the capability registers are enabled. |

| Enable control and status registers | On/Off | Enables soft registers for reading status signals and writing control signals on the PHY interface through the embedded debug. Refer to the PMA/PMA Interface Avalon® Memory-Mapped Interface Registers section. |

| Configuration file prefix | File prefix | Specifies the file prefix to use for generated configuration files when enabled. Each variant of the IP should use a unique prefix for configuration files. |

| Generate SystemVerilog package file | On/Off | When enabled, The IP generates a SystemVerilog package file named [Configuration file prefix]_reconfig_parameters.sv containing parameters defined with the attribute values needed for reconfiguration. |

| Generate C header file | On/Off | When enabled, The IP generates a C header file named [Configuration file prefix]_reconfig_parameters.h containing macros defined with the attribute values needed for reconfiguration. |

| Generate MIF (Memory Initialize File) | On/Off | When enabled, the IP generates a Memory Initialization File (MIF) named [Configuration file prefix]_reconfig_parameters.mif. The MIF file contains the attribute values needed for reconfiguration in a data format. |

| Enable multiple reconfiguration profiles | On/Off | When enabled, you can use the GUI to store multiple configurations. The IP generates reconfiguration files for all of the stored profiles. The IP also checks your multiple reconfiguration profiles for consistency to ensure you can reconfigure between them. |

| Enable embedded reconfiguration streamer | On/Off | Enables the embedded reconfiguration streamer, which automates the dynamic reconfiguration process between multiple predefined configuration profiles. |

| Generate reduced reconfiguration files | On/Off | When enabled, the Native PHY generates reconfiguration report files containing only the attributes or RAM data that are different between the multiple configured profiles. |

| Number of reconfiguration profiles | 1 - 8 | Specifies the number of reconfiguration profiles to support when multiple reconfiguration profiles are enabled. |

| Store current configuration to profile | On/Off | Selects which reconfiguration profile to store when clicking the Store profile button. |

| rcfg_profile_data0 | Profile data | Dynamic reconfiguration parameter data for Profile 0. |

| rcfg_profile_data1 | Profile data | Dynamic reconfiguration parameter data for Profile 1. |

| rcfg_profile_data2 | Profile data | Dynamic reconfiguration parameter data for Profile 2. |

| rcfg_profile_data3 | Profile data | Dynamic reconfiguration parameter data for Profile 3. |

| rcfg_profile_data4 | Profile data | Dynamic reconfiguration parameter data for Profile 4. |

| rcfg_profile_data5 | Profile data | Dynamic reconfiguration parameter data for Profile 5. |

| rcfg_profile_data6 | Profile data | Dynamic reconfiguration parameter data for Profile 6. |

| rcfg_profile_data7 | Profile data | Dynamic reconfiguration parameter data for Profile 7. |