Visible to Intel only — GUID: nik1412546873302

Ixiasoft

Visible to Intel only — GUID: nik1412546873302

Ixiasoft

5.2.7. Splitting the SOF File for the CvP Initialization Mode with the CvP Revision Design Flow

To implement the CvP Revision Design Flow in CvP initialization mode, you must replace the base .sof (top.sof) with the revision .sof (cvp_app1.sof). You must also specify a different file name for the CvP revision. This example uses cvp_app.jic. The periphery and the core images created for the CvP revision are cvp_app.periph.jic and cvp_app.core.rbf, respectively. Follow these steps to create the periphery and core images for the CvP revision:

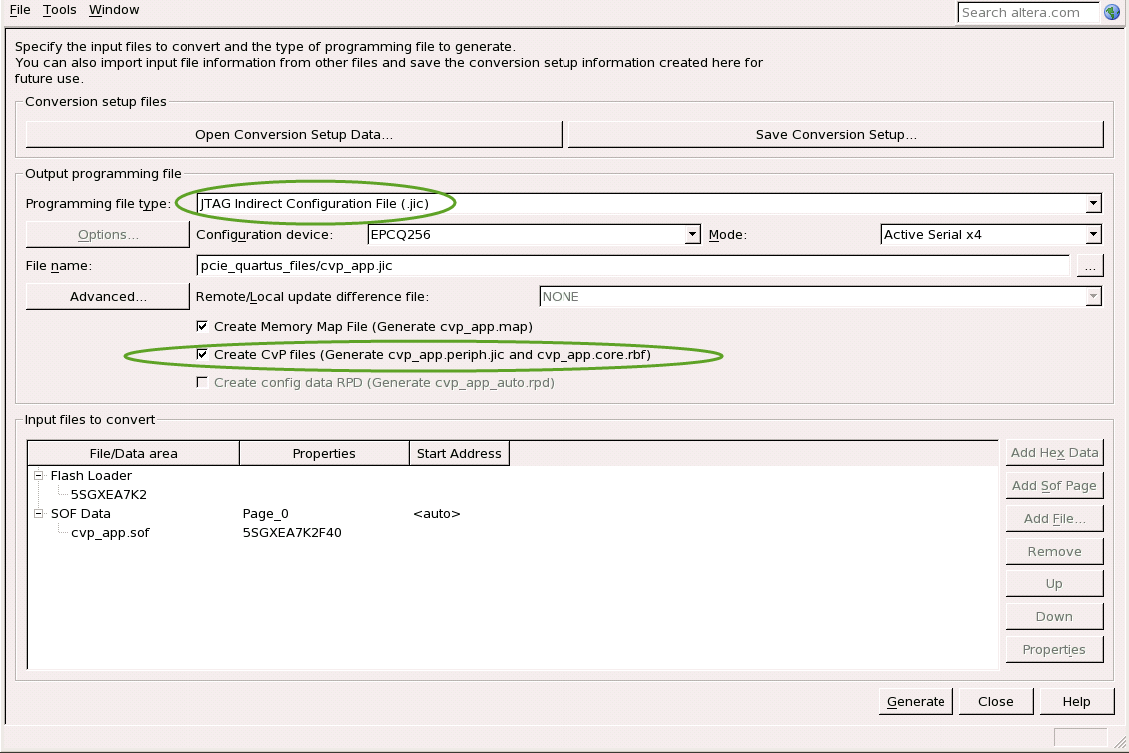

- On the File menu, select Convert Programming File. Under Output programming file specify the options in the following table. These settings are illustrated in the figure below.

Table 16. CvP Revision Design Flow: Output Programming File Options Parameter

Value

Programming file type

JTAG Indirect Configuration File (.jic)

Configuration device

EPCQ256

Mode

Active Serial x4

File name

Click browse and specify pcie_quartus_files/cvp_app.jic

Create Memory Map File

Turn this option on.

Create CvP files

Turn this option on. This box is greyed out until you specify the SOF Data file under Input files to convert.

- Under Input files to convert specify the options in the following table:

Table 17. CvP Revision Design Flow: Input Files to Convert Parameter

Value

Flash Loader

Click Add Device and select Stratix V and then 5SGXEA7K2.

Click SOF Data

Click Add File and navigate to ./pcie_quartus_files/cvp_app.sof. If you specified a compressed or encrypted bitstream in the Device and Pin Options dialog box, you must specify the same options in the Conversion Programming File window. To enable these settings, click cvp_app.sof , then click Properties and check the appropriate boxes.

- Turn on the Create CvP files (Generate cvp_app1.periph.jic and cvp_app1.core.rbf) parameter in the Output Programming Files section.

- To save the Conversion Programming File parameters, click Save Conversion Setup and type an output file name. Saving your conversion setup saves time on subsequent conversions. For this exercise, call your settings cvp_revision.cof. You can reload the conversion parameters by opening the Conversion Setup File ( *.cof) using Open Conversion Setup Data in the Convert Programming File window. The following figure illustrates these options.

- Click Generate. This conversion process creates the alternate core logic, cvp_app.core.rbf, and the periphery logic, cvp_app.periph.jic. The periphery logic, cvp_app.periph.jic, should be identical to the periphery logic created when splitting the base revision.

Note: The generated CvP peripheral file size matches the size of the configuration device chosen.Figure 34. CvP Revision Design Flow: Convert Programming Files

- Proceed to Bringing Up the Hardware.

The file top.cof provided in *_cvp * designs is a template for CvP initialization mode. You can open this file in the Open Conversion Setup Data of Convert Programming File window to retrieve the parameters shown in figure above.