Visible to Intel only — GUID: nik1412546916495

Ixiasoft

Visible to Intel only — GUID: nik1412546916495

Ixiasoft

5.3.7. Splitting the SOF File for the CvP Update Design Mode

Follow these steps to split your to create file into periphery and core images for CvP update mode. You use the core image, top.core.rbf, to perform CvP updates.

- On the File menu, select Convert Programming File.

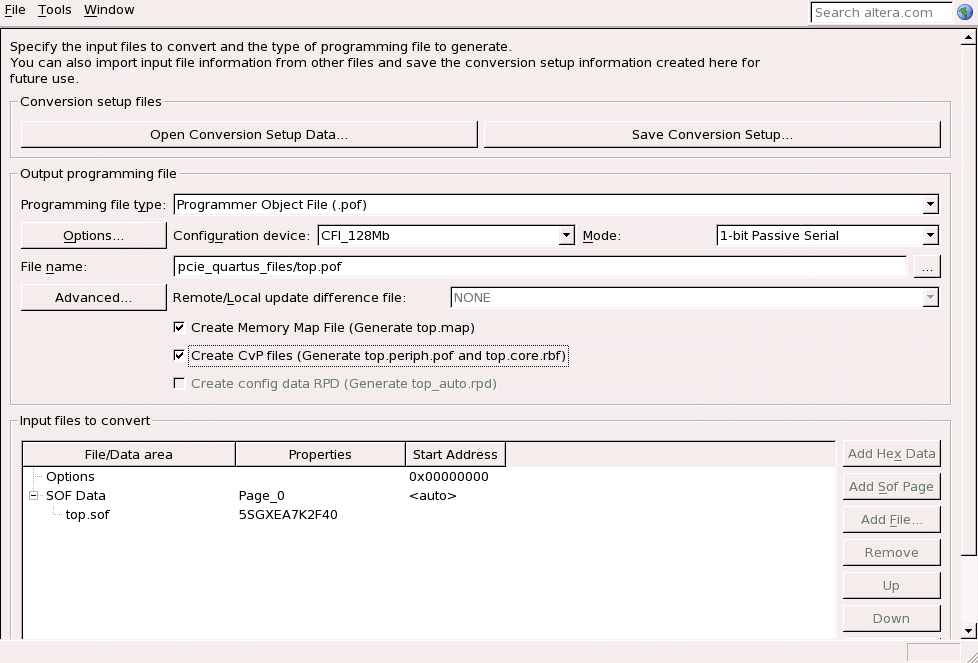

- Under Output programming file specify the options in the following table. These options are illustrated in the figure below.

Table 21. Output Programming File Parameter

Value

Programming file type

Programmer Object File (.pof)

Configuration device

CFI_128Mb

Mode

1-bit Passive Serial

File name

Click browse and specify pcie_quartus_files/top.pof.

Create Memory Map File

Turn this option on.

Create CvP files

Turn this option on. This box is greyed out until you specify the SOF Data file under Input files to convert.

- Under Input files to convert specify the options in the following table:

Table 22. Input files to convert Parameter

Value

Click SOF Data

Click Add File and navigate to ./pcie_quartus_files/top.sof. If you specified a compressed or encrypted bitstream in the Device and Pin Options dialog box, you must specify the same options in the Conversion Programming File window. To enable these settings, click top.sof, then click Properties and check the appropriate boxes.

- Turn on the Create CvP files (Generate top.periph.jic and top.core.rbf) parameter in the Output Programming Files section.

- Click Generate to create top.periph.pof, and top.core.rbf. The periphery file, top.periph.pof is generated, but it is not used.