Visible to Intel only — GUID: nik1409872356812

Ixiasoft

Visible to Intel only — GUID: nik1409872356812

Ixiasoft

2.2.2.1. Non-Bonded Channel Configurations

| Clock Line | Transmitter PLL | Clock Path |

|---|---|---|

| x1 | ATX PLL23 | ATX PLL » x1 » individual clock divider » serializer |

| CMU | CMU PLL » x1 » individual clock divider » serializer | |

| fPLL | fPLL » x1_fPLL » individual clock divider » serializer | |

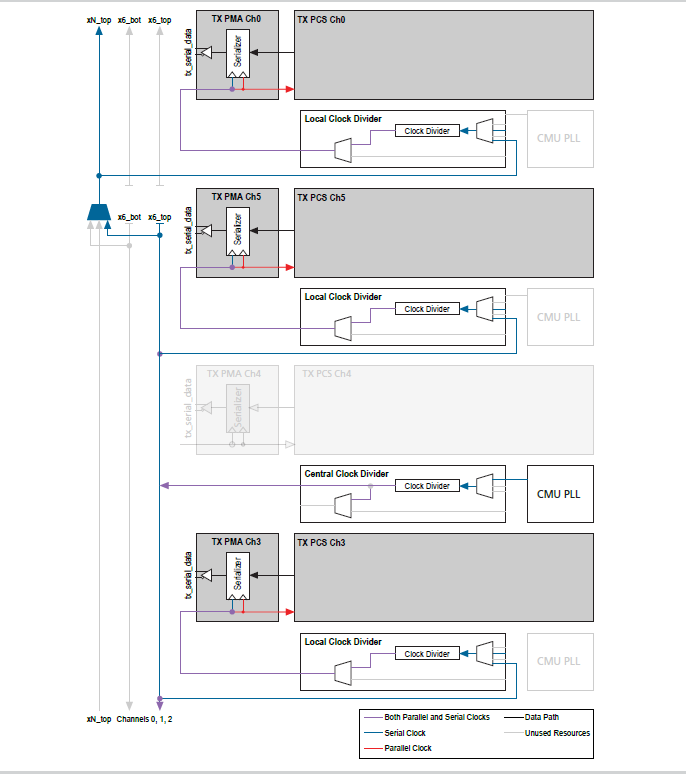

| x6, xN | ATX PLL23 | ATX PLL » central clock divider » x6 » xN » individual clock divider » serializer |

| CMU | CMU PLL » central clock divider » x6 » xN » individual clock divider » serializer 24 | |

| fPLL | fPLL » x1_fPLL » central clock divider » x6 » individual clock divider » serializer 24 |

When the fPLL is used to drive more than three non-bonded channels, the channel where the central clock divider resides adjacent to the fPLL cannot be used as a transmitter. The fPLL uses a central clock divider to access the x6 clock network when driving more than three non-bonded channels, so the divider is no longer available to implement a transmitter. For xN non-bonded configurations, the ch 1 or ch 4 transceiver bank where the central clock divider resides cannot be used as a data channel since the parallel clock cannot be generated in this channel.