Visible to Intel only — GUID: sfo1410068393091

Ixiasoft

Visible to Intel only — GUID: sfo1410068393091

Ixiasoft

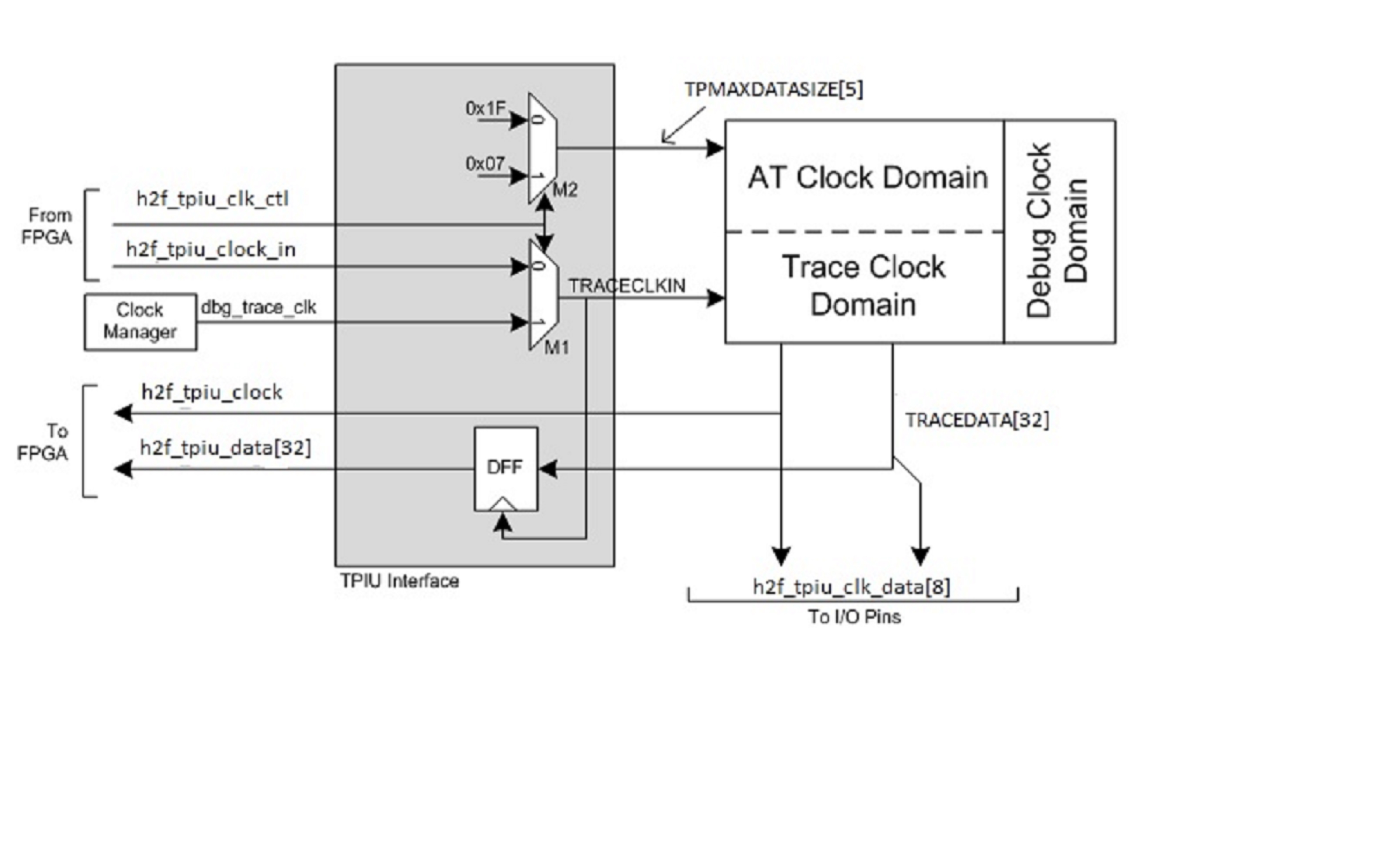

11.4.10.4. TPIU

| Signal | Description |

|---|---|

| h2f_tpiu_clk_ctl | Selects whether trace data is captured using the internal TPIU clock, which is the dbg_trace_clk signal from the clock manager; or an external clock provided as an input to the TPIU from the FPGA. 0 - use h2f_tpiu_clock_in 1 - use internal clock Note: When the FPGA is powered down or not configured the TPIU uses the internal clock. |

| h2f_tpiu_data[32] | 32 bit trace data bus to the FPGA. Trace data changes on both edges of h2f_tpiu_clock. Note: When the FPGA is powered down or not configured, the TPIU sends the lower 8-bits trace data to I/Os. |

| h2f_tpiu_clock_in | Clock from the FPGA used to capture trace data. |

| h2f_tpiu_clock | Clock output from TPIU |